Testing Issues

Posted: Tue Dec 26, 2017 3:07 pm

Just bought and received DSO112A.

Some observations -

1) Using your test signal at 100 Khz, time base 1 uS or 2 uS or 5uS display will not be stable.

Only when selected 10 uS or higher will I get a stable display. Waveform 7 divisions high,

vert at .5 Vdc, Normal triggering

2) Using your test signal at 100 Khz, time base 1 uS, trying to see leading edge of test signal,

I should see 5 Mhz sample rate / 100 Khz signal = 50 samples. I see no stable display.

3) Using test signal at 1 Mhz, Tektronix 1 GS/sec scope TDS754A, 10X probe compensated

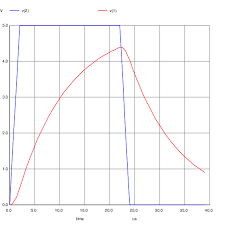

on Tek scope, I see not a square wave but a severely distorted RC rise and fall waveform.

Why is this not a high drive CMOS output on the processor ? So thats its square ?

4) Using your 1 Mhz test signal the DSO112A will not trigger at any timebase setting ? It has

5 Mhz sample rate, why is it not triggering at all.

5) How do I tell what version of firmware I have ? What DSO112A screen is it stated on ?

6) Any plans to upgrade with signal averaging, envelope mode, and FFT ? Signal averaging (noise reduction)

the most important, followed by envelope (jitter measurements) followed by FFT for spectrum studies.

Regards, Dana.

Some observations -

1) Using your test signal at 100 Khz, time base 1 uS or 2 uS or 5uS display will not be stable.

Only when selected 10 uS or higher will I get a stable display. Waveform 7 divisions high,

vert at .5 Vdc, Normal triggering

2) Using your test signal at 100 Khz, time base 1 uS, trying to see leading edge of test signal,

I should see 5 Mhz sample rate / 100 Khz signal = 50 samples. I see no stable display.

3) Using test signal at 1 Mhz, Tektronix 1 GS/sec scope TDS754A, 10X probe compensated

on Tek scope, I see not a square wave but a severely distorted RC rise and fall waveform.

Why is this not a high drive CMOS output on the processor ? So thats its square ?

4) Using your 1 Mhz test signal the DSO112A will not trigger at any timebase setting ? It has

5 Mhz sample rate, why is it not triggering at all.

5) How do I tell what version of firmware I have ? What DSO112A screen is it stated on ?

6) Any plans to upgrade with signal averaging, envelope mode, and FFT ? Signal averaging (noise reduction)

the most important, followed by envelope (jitter measurements) followed by FFT for spectrum studies.

Regards, Dana.